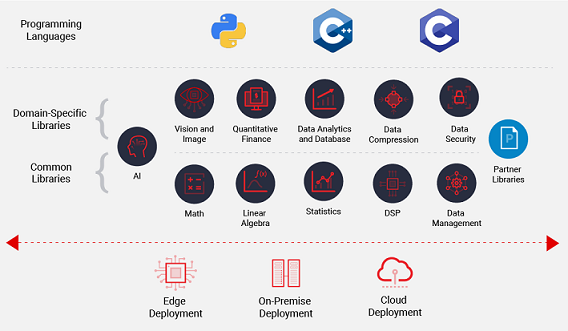

Vitis™ Unified Software Platform includes an extensive set of open-source, performance-optimized libraries that offer out-of-the-box acceleration with minimal to zero-code changes to your existing applications.

- Common Vitis accelerated-libraries for Math, Statistics, Linear Algebra, and DSP offer a set of core functionality for a wide range of diverse applications.

- Domain-specific Vitis accelerated libraries offer out-of-the-box acceleration for workloads like Vision and Image Processing, Quantitative Finance, Database, and Data Analytics, Data Compression and more.

- Leverage the rich growing ecosystem of partner-accelerated libraries, framework plug-ins, and accelerated applications to hit the ground running and accelerate your path to production.

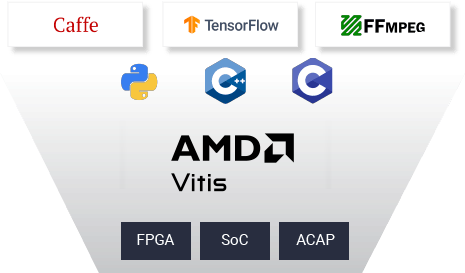

Use Vitis accelerated-libraries in commonly-used programming languages that you know like C, C++, and Python. Leverage Xilinx platforms as an enabler in your applications – Work at an application level and focus your core competencies on solving challenging problems in your domain, accelerate time to insight, and innovate.

Whether you want to accelerate portions of your existing x86 host application code or want to develop accelerators for deployment on Xilinx embedded platforms, calling a Vitis accelerated-library API or Kernel in your code offers the same level of abstraction as any software library.

Vitis accelerated-libraries are accessible to all developers through GitHub and scalable across all Xilinx platforms. Develop your applications using these optimized libraries and seamlessly deploy across Xilinx platforms at the edge, on-premise or in the cloud without having to reimplement your accelerated application.

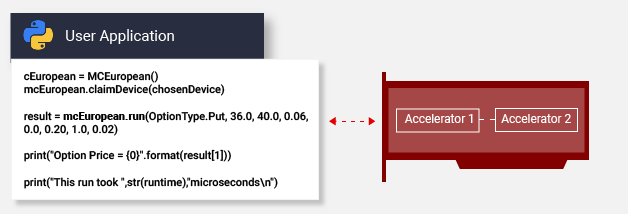

For rapid prototyping and quick evaluation of the benefits Xilinx can bring to your applications, you can use them as plug-and-play accelerators, called directly as an API in the user application for several workloads like Computer Vision and Image Processing, Quantitative Finance, Database, and Data Analytics among others.

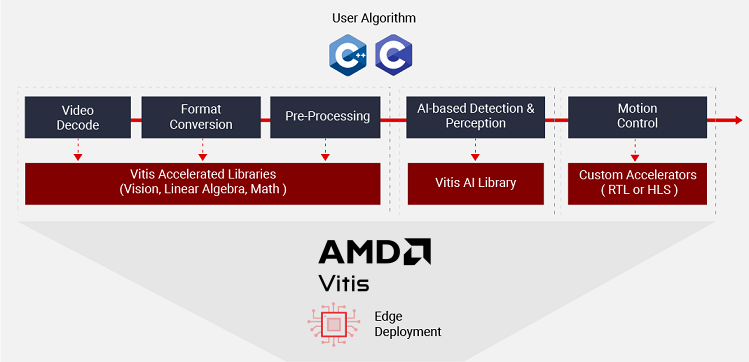

To design custom accelerators for your application, use Vitis library functions as optimized algorithmic building blocks, modify them to suit your specific needs, or use them as a reference to completely design your own. Choose the flexibility you need!

Combine domain-specific Vitis libraries with pre-optimized deep learning models from the Vitis AI library or the Vitis AI development kit to accelerate your whole application and meet the overall system-level functionality and performance goals.